# Energy Efficient CRC Design for Processor of Workstation, and Server using LVCMOS

#### Abhay Saxena<sup>1\*</sup>, Chandrashekhar Patel<sup>1</sup> and M. Sadiq Ali Khan<sup>2</sup>

<sup>1</sup>Dev Sanskriti Vishvavidyalaya, Haridwar - 249411, Uttarakhand, India; abhaysaxena2009@gmail.com, shekharrockin1988@gmail.com <sup>2</sup>Department of Computer Science, University of Karachi, Pakistan; msakhan@uok.edu.pk

#### Abstract

In our work we have designed CRC using the LVCMOS IO standards which are stands for Low Voltage Complementary Metal Oxide Semiconductor. In this work we have worked with four kinds of LVCMOS (LVCMOS 12, LVCMOS 15, LVCMOS 18, LVCMOS 25). For LVCMOS 12 when we scaled down the frequency form 50GHz to 10 GHz we found 64.41% reduction in total power. For LVCMOS 15 when we change down the frequency form 50GHz to 10GHz we found 67.58% reduction in total power. For LVCMOS 18 when we scaled down the frequency form 50GHz to 10 GHz we found 69.54% reduction in total power. In last when we reduced the frequency form 50GHz to 10GHz we found 64.41% reduction in total power. Our CRC design is implemented on Virtex-6 FPGA family.

Keywords: 40 nm FPGA, CRC, Energy Efficient, Low Power, LVCMOS IO Standard

## 1. Introduction

In networking when we send data form one system to another system then we always try to ensure that receiver always get error free data. For that we can apply error detection techniques.

CRC is an error detection technique which is stands for Cyclic Redundancy Check, through CRC we can detect the error but we cannot resolve or correct the data.

In these techniques we append some check bits also called checksum to the message and send it to the receiver. After receiving the data receiver verified the checksum with data and assert that error would occur or not. If there is an error then receiver sends Negative Acknowledgment (NCK) to sender for retransmission of the packets.

In our paper we have design 8 bit CRC Polynomial which is also called CRC-8-CCITT. Equation (1) shows our CRC polynomial equation and figure 1 shows the circuit diagram generated by our polynomial.

$$P(x) = x^8 + x^2 + x^1 + x^0$$

(1)

Figure 1. Circuit diagram of CRC polynomial.

Figure 2. Top Level of schematic of CRC.

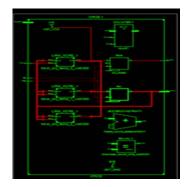

Figure 3. RTL schematic of CRC.

In Figure 3 and Figure 4 we have shown the Top Level of Schematic of CRC and RTL Schematic of CRC.

## 2. Related Work

There is 67.04% dynamic power reduction with LVCMOS12<sup>2</sup>. There is 85.18% power reduction when we migrate from LVCMOS33 based ALU design to LVCMOS12 based ALU design<sup>3</sup>. 28nm technology based FPGA deliver energy efficient design<sup>3,4</sup>. LVCMOS is not only used in energy efficient design of ALU<sup>2,3</sup> but also in energy efficient Sindhi unicode reader<sup>4</sup>, thermal aware energy efficient Vedic multiplier<sup>5</sup>, power optimization of pseudo noise based optical transmitter<sup>6</sup>, energy efficient solar charge sensor<sup>7</sup> and energy efficient energy efficient Frequency Meter<sup>8</sup>.

### 3. Results

We have opted VHDL language to design CRC and implemented it on Virtex-6 family.

Table 1.Power consumption at LVCMOS12

|        | Clock | Logic | Signals | IOs   | Leakage | Total |

|--------|-------|-------|---------|-------|---------|-------|

|        |       |       |         |       |         | Power |

| 10 GHz | 0.349 | 0.007 | 0.030   | 0.668 | 1.315   | 2.370 |

| 20 GHz | 0.698 | 0.010 | 0.058   | 1.336 | 1.340   | 3.442 |

| 30 GHz | 1.047 | 0.012 | 0.086   | 2.005 | 1.365   | 4.514 |

| 40 GHz | 1.395 | 0.014 | 0.113   | 2.673 | 1.392   | 5.587 |

| 50 GHz | 1.744 | 0.015 | 0.140   | 3.341 | 1.420   | 6.661 |

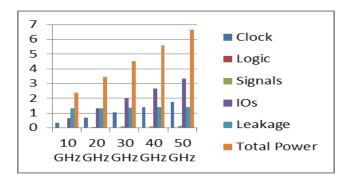

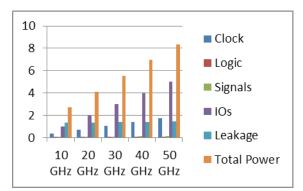

In the Table 1 we have worked with LVCMOS12. In this table we found that when we migrate from 50GHz to 10 GHz then we reduce the power consumption by 64.41%.We have also converted this data through bar graph as shown in Figure 4.

Figure 4. Power analysis at LVCMOS 12.

Table 2.

Power consumption at LVCMOS15

|        | Clock | Logic | Signals | IOs   | Leakage | Total |

|--------|-------|-------|---------|-------|---------|-------|

| _      |       |       |         |       |         | Power |

| 10 GHz | 0.349 | 0.007 | 0.030   | 0.998 | 1.323   | 2.708 |

| 20 GHz | 0.698 | 0.010 | 0.058   | 1.996 | 1.356   | 4.118 |

| 30 GHz | 1.047 | 0.012 | 0.086   | 2.993 | 1.391   | 5.528 |

| 40 GHz | 1.395 | 0.014 | 0.113   | 3.991 | 1.427   | 6.941 |

| 50 GHz | 1.744 | 0.015 | 0.140   | 4.989 | 1.466   | 8.355 |

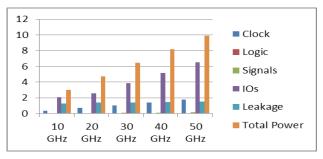

In the Table 2 we have worked with LVCMOS15. In this table we found that when we migrate from 50GHz to 10 GHz then we reduce the power consumption by 67.58%. We have also converted this data through bar graph as shown in Figure 5.

Figure 5. Power analysis at LVCMOS 15.

Table 3.

Power consumption at LVCMOS 18

|        | Clock | Logic | Signals | IOs   | Leakage | Total |

|--------|-------|-------|---------|-------|---------|-------|

|        |       |       |         |       |         | Power |

| 10 GHz | 0.349 | 0.007 | 0.030   | 2.088 | 1.298   | 3.015 |

| 20 GHz | 0.698 | 0.010 | 0.058   | 2.596 | 1.371   | 4.733 |

| 30 GHz | 1.047 | 0.012 | 0.086   | 3.893 | 1.415   | 6.452 |

| 40 GHz | 1.395 | 0.014 | 0.113   | 5.191 | 1.461   | 8.174 |

| 50 GHz | 1.744 | 0.015 | 0.140   | 6.489 | 1.510   | 9.900 |

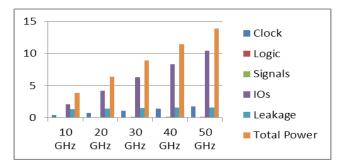

In the Table 3 we have worked with LVCMOS18. In this table we found that when we migrate from 50GHz to10GHz then we reduce the power consumption by 69.54%. We have also converted this data through bar graph as shown in Figure 6

Figure 6. Power analysis at 3GHz.

Table 4.Power consumption at LVCMOS 25

|        | Clock | Logic | Signals | IOs    | Leakage | Total  |

|--------|-------|-------|---------|--------|---------|--------|

|        |       |       |         |        |         | Power  |

| 10 GHz | 0.349 | 0.007 | 0.030   | 2.088  | 1.350   | 3.825  |

| 20 GHz | 0.698 | 0.010 | 0.058   | 4.177  | 1.413   | 6.356  |

| 30 GHz | 1.047 | 0.012 | 0.086   | 6.265  | 1.482   | 8.891  |

| 40 GHz | 1.395 | 0.014 | 0.113   | 8.354  | 1.558   | 11.433 |

| 50 GHz | 1.744 | 0.015 | 0.140   | 10.442 | 1.605   | 13.947 |

In the Table 4 we have worked with LVCMOS12. In this table we found that when we migrate from 50GHz to 10 GHz then we reduce the power consumption by 72.57%. We have also converted this data through bar graph as shown in Figure 7.

Figure 7. Power Analysis at 3GHz.

## 4. Conclusion

In our work we have calculated total power consumption using different-different family of LVCMOS (LVCMOS12, LVCMOS15, LVCMOS18, LVCMOS25) at differentdifferent frequency. We found that LVCMOS 12 is most energy efficient IO standard compare to other LVCMOS IO standard. We also found that there is no change in Logic, Signal and IOs.

## 5. Future Scope

In this work, CRC Design is implemented on Virtex-6, but we have a scope to redesign this CRC on latest 65nm Virtex-5 and 40nm Virtex-6, 90nm Virtex-4 FPGA to make the most energy efficient CRC for data transmission. Instead of LVCMOS IO standards we can use other IO standards like SSTL and LVDCI.

## 6. Acknowledgment

The author would like to acknowledge Gyancity Research Lab (India and Overseas) for their valuable support for the findings of this research paper.

## 7. References

- CRC polynomial. Available from: http://ghsi.de/CRC/index.php

- Pandey B, Yadav J, Singh YK, Kumar R, Patel S. Energy efficient design and implementation of ALU on 40nm FPGA. 2013 International Conference on Energy Efficient Technologies for Sustainability (ICEETS); 2013. p. 45–50.

- Pandey B, Yadav J, Pattanaik M. IO standard based energy efficient ALU design and implementation on 28nm FPGA. 2013 Annual IEEE India Conference (INDICON); 2013. p. 1–5.

- Madhok S, Kaur I, Taxali V, Thind V, Dabas S, Madhok T. LVCMOS based energy efficient Sindhi unicode reader for natural processing on 28nm FPGA. International Journal of u- and e-Service, Science and Technology. 2015; 8(8).

- Goswami K, Pandey B. LVCMOS based thermal aware energy efficient vedic multiplier design on FPGA. 2014 International Conference on Computational Intelligence and Communication Networks (CICN); 2014. p. 921–4.

- Das B, Kiyani A, Kumar V, Abdullah MFL, Pandey B. Power optimization of pseudo noise based optical transmitter using LVCMOS IO standard. Power Generation System and Renewable Energy Technologies (PGSRET); 2015. p. 1–7.

- Singla A, Kaur A, Pandey B. LVCMOS based energy efficient solar charge sensor design on FPGA. 2014 IEEE 6th India International Conference on Power Electronics (IICPE); 2014. p. 1–5.

- Kumar T, Pandey B, Das T. LVCMOS I/O standard and drive strength based energy efficient design on ultra scale FPGA. 2013 International Conference on Green Computing, Communication and Conservation of Energy (IC-GCE); 2013. p. 116–9.